P4 in SDN-based Attack Detection and AI-driven Security Mechanisms

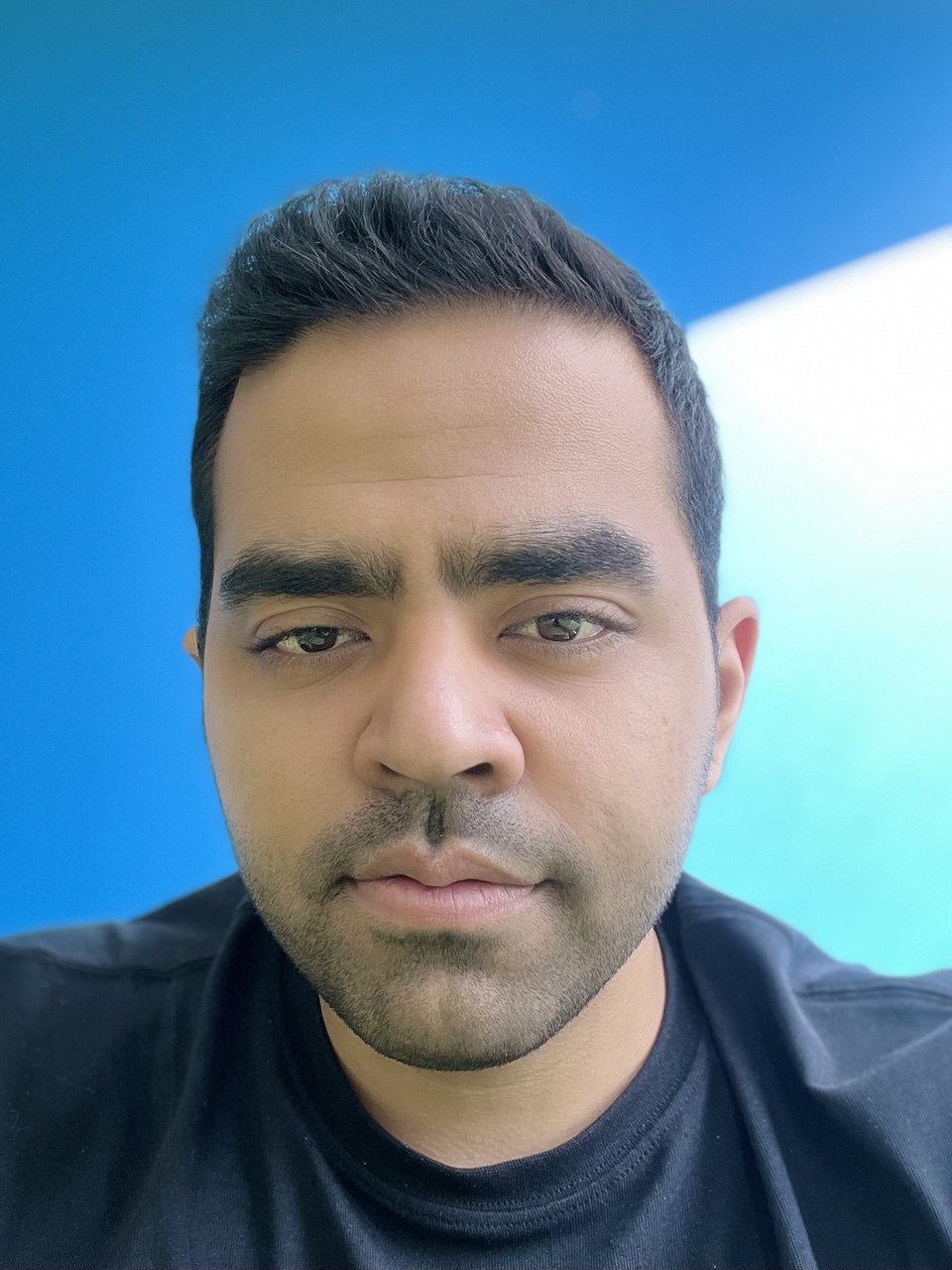

Reza Fallahi Kapourchali | May 6, 2025

Abstract

Software-Defined Networking (SDN) is a promising network architecture that offers greater flexibility and scalability compared to traditional network infrastructures. This flexibility arises from the separation of the data plane from the control plane, which enables the use of general-purpose devices, commonly referred to as “dumb devices” in SDN. While this separation enhances network management and administration, it also imposes processing limitations, leading to increased overhead on the controller. This is precisely where P4, a domain-specific programming language for packet processing, becomes highly beneficial.

In the field of network security, particularly in attack detection, researchers have proposed various innovative methods. P4 can play a crucial role in advancing these solutions by leveraging a programmable data plane to offload processing tasks from the controller, thereby achieving a more balanced distribution of computational load between the data and control planes. One of the most critical areas of application in this regard is the detection and mitigation of Distributed Denial-of-Service (DDoS) attacks.

Additionally, there has been a significant rise in AI-based security solutions, with machine learning (ML) being a prominent subfield. ML enables the development of custom AI agents tailored for specific tasks, requiring the extraction of relevant features for training purposes. However, without a programmable data plane, this approach is impractical in both SDN and traditional networks. With P4, however, such implementations become feasible, opening new possibilities for AI-driven network security solutions.

In this webinar, we will explore the use cases of P4 in SDN-based attack detection and AI-driven security mechanisms, highlighting its potential to enhance modern network security strategies.