# SmartNICs – P4's Final Latest Frontier

## Challenges and Opportunities Ahead

Mario Baldi Fellow, AMD Research and Advanced Development

7<sup>th</sup> European P4 Workshop (EuroP4 '24)

AMD together we advance\_

#### P4: The Origin

#### P4: Programming Protocol-Independent Packet Processors

Pat Bosshart<sup>†</sup>, Dan Daly<sup>\*</sup>, Glen Gibb<sup>†</sup>, Martin Izzard<sup>†</sup>, Nick McKeown<sup>‡</sup>, Jennifer Rexford<sup>\*\*</sup>, Cole Schlesinger<sup>\*\*</sup>, Dan Talayco<sup>†</sup>, Amin Vahdat<sup>¶</sup>, George Varghese<sup>§</sup>, David Walker<sup>\*\*</sup> <sup>†</sup>Barefoot Networks <sup>\*</sup>Intel <sup>‡</sup>Stanford University <sup>\*\*</sup>Princeton University <sup>¶</sup>Google <sup>§</sup>Microsoft Research

#### ABSTRACT

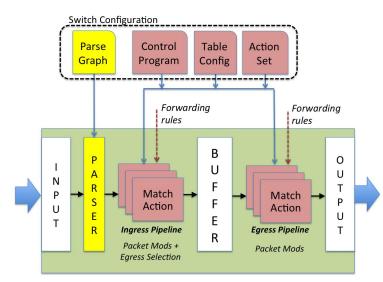

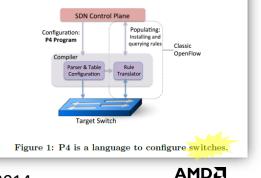

P4 is a high-level language for programming protocol-independent packet processors. P4 works in conjunction with SDN control protocols like OpenFlow. In its current form, OpenFlow explicitly specifies protocol headers on which it operates. This set has grown from 12 to 41 fields in a few vears, increasing the complexity of the specification while still not providing the flexibility to add new headers. In this paper we propose P4 as a strawman proposal for how Open-Flow should evolve in the future. We have three goals: (1) Reconfigurability in the field: Programmers should be able to change the way switches process packets once they are deployed. (2) Protocol independence: Switches should not be tied to any specific network protocols. (3) Target independence: Programmers should be able to describe packetprocessing functionality independently of the specifics of the underlying hardware. As an example, we describe how to use P4 to configure a switch to add a new hierarchical label.

#### 1. INTRODUCTION

Software-Defined Networking (SDN) gives operators programmatic control over their networks. In SDN, the control plane is physically separate from the forwarding plane, and one control plane controls multiple forwarding devices. While forwarding devices could be programmed in many ways, having a common, open, vendor-agnostic interface (like OpenFlow) enables a control plane to control forwarding devices from different hardware and software vendors. multiple stages of rule tables, to allow switches to expose more of their capabilities to the controller.

The proliferation of new header fields shows no signs of stopping. For example, data-center network operators increasingly want to apply new forms of packet encapsulation (e.g., NVGRE, VXLAN, and STT), for which they resort to deploying software switches that are easier to extend with new functionality. Rather than repeatedly extending the OpenFlow specification, we argue that future switches should support flexible mechanisms for parsing packets and matching header fields, allowing controller applications to leverage these capabilities through a common, open interface (i.e., a new "OpenFlow 2.0" API). Such a general, extensible approach would be simpler, more elegant, and more future-proof than today's OpenFlow 1.x standard.

together we advance\_

SIGCOMM 2014

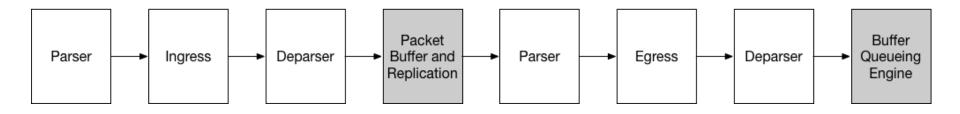

### P4 Community – Portable Switch Architecture (PSA)

p4.org Architecture Working Group Specification: **P4<sub>16</sub> Portable Switch Architecture (PSA)** https://p4.org/p4-spec/docs/PSA-v1.2.html#sec-target-architecture-model

AMD together we advance\_

3

#### **The First Available Products: Indeed Switches**

# Intel/Barefoot Tofino

https://www.intel.cn/content/www/cn/zh/products/network-io/programmable-ethernet-switch.html

5

AMD together we advance\_

#### **More Switching Products Followed**

# **Cisco Silicon One**

https://www.cisco.com/c/en/us/solutions/collateral/siliconone/datasheet-c78-744834.html

together we advance\_

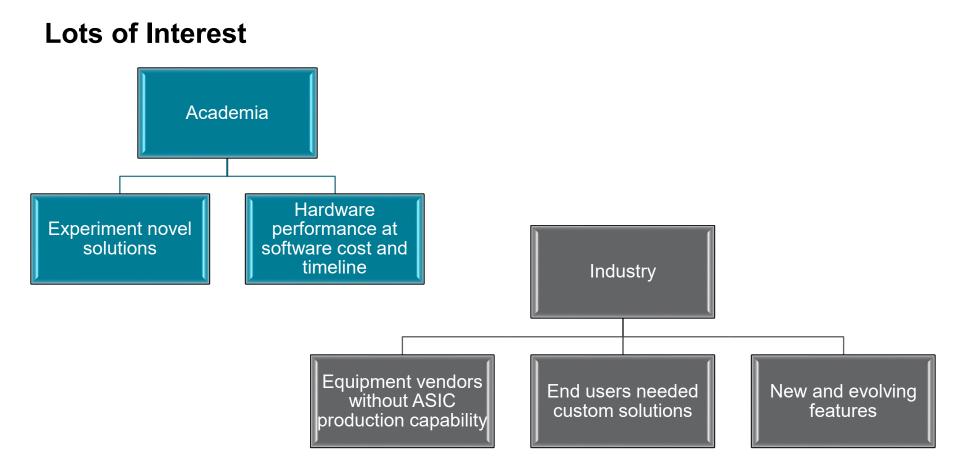

## **Big Fans: Cloud Providers and Hyperscalers**

AMD together we advance\_

#### Portable NIC Architecture (PNA) v0.7

p4.org Architecture Workgroup Specification https://p4.org/p4-spec/docs/PNA-v0.7.0.html#sec-introduction

#### Standard programmable interface to the host AMD T together we advance\_

11

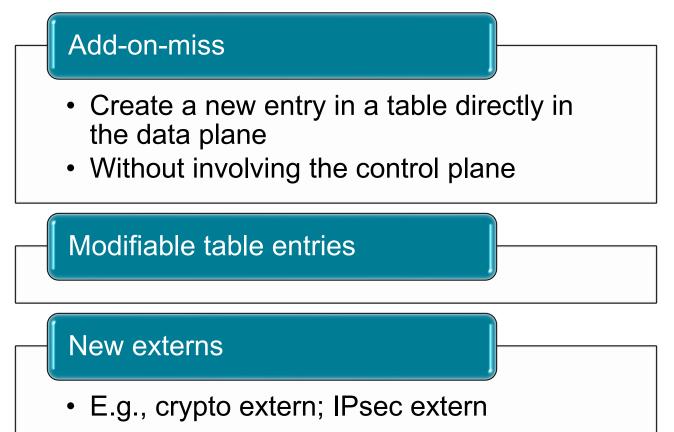

#### **PNA Novelties**

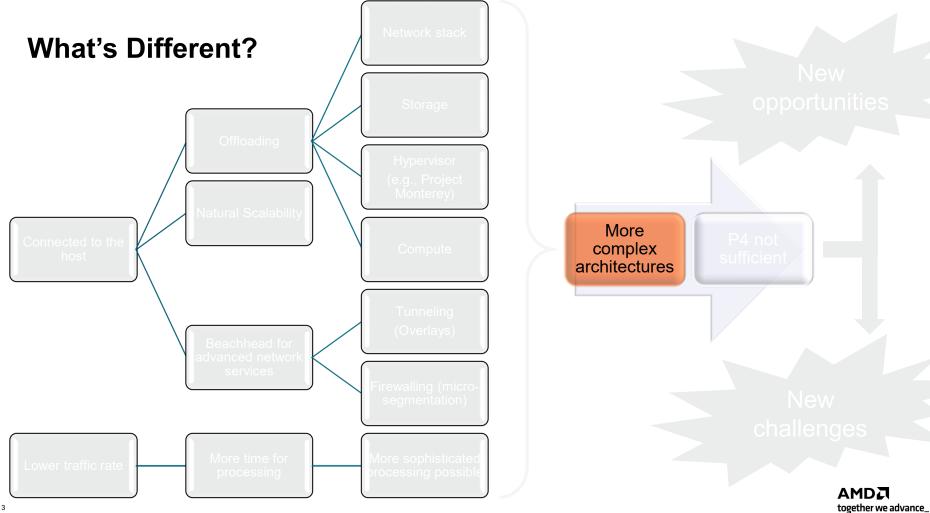

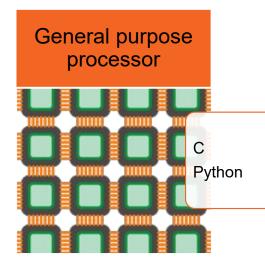

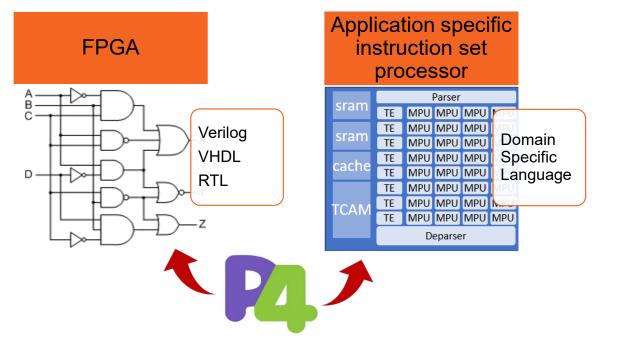

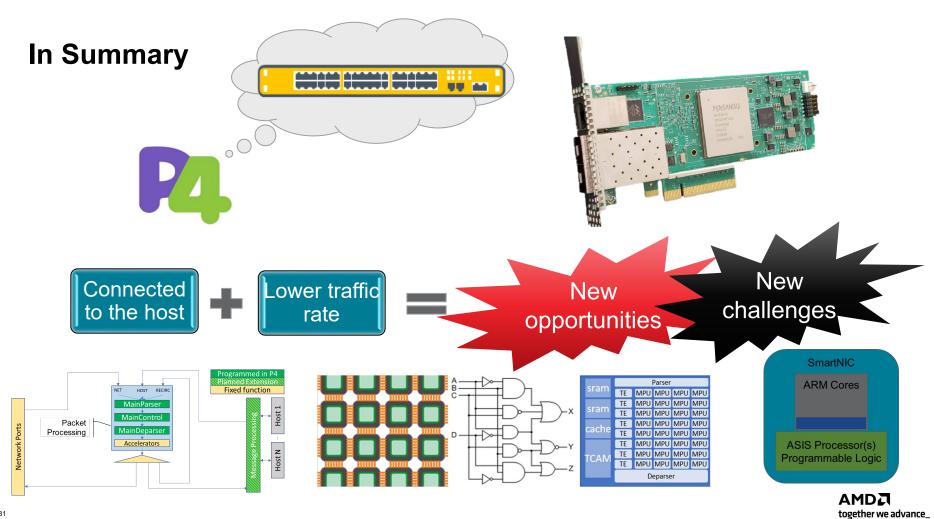

#### Various Processing Technologies, Different Languages

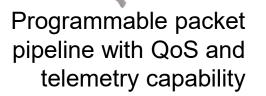

## Available SmartNIC Options

## Fully Programmable FPGA-based SmartNICs

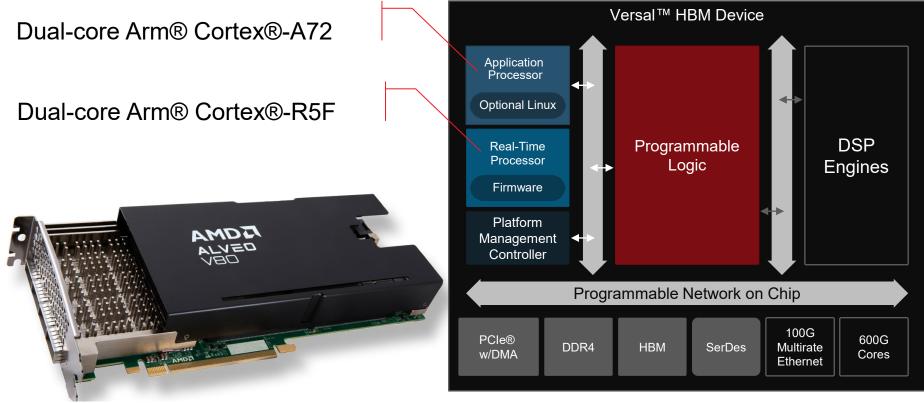

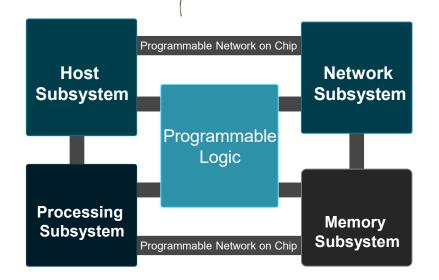

### FPGA + arm Cores: Alveo™ V80

AMD together we advance\_

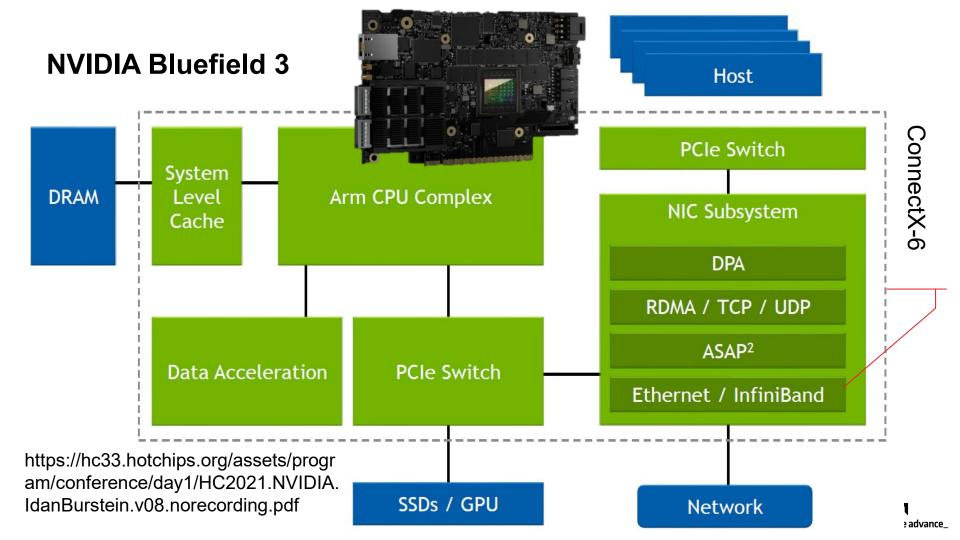

## A hybrid approach: fixed functions and (P4) Programmable The AMD 400G Adaptive SmartNIC SoC

- 2x200 Gbps Ethernet

- 16 lanes PCIe Gen 5

- Hardened logic for

- Maximum performance

- Minimum latency

- Maximum power efficiency

- Large FPGA for custom functionality

- Cloud providers and AI

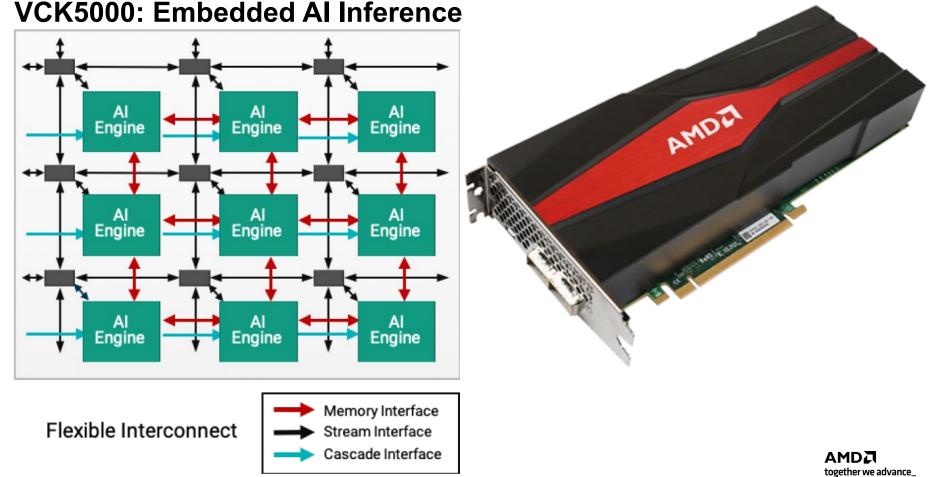

#### VCK5000: Embedded Al Inference

Want to Try?

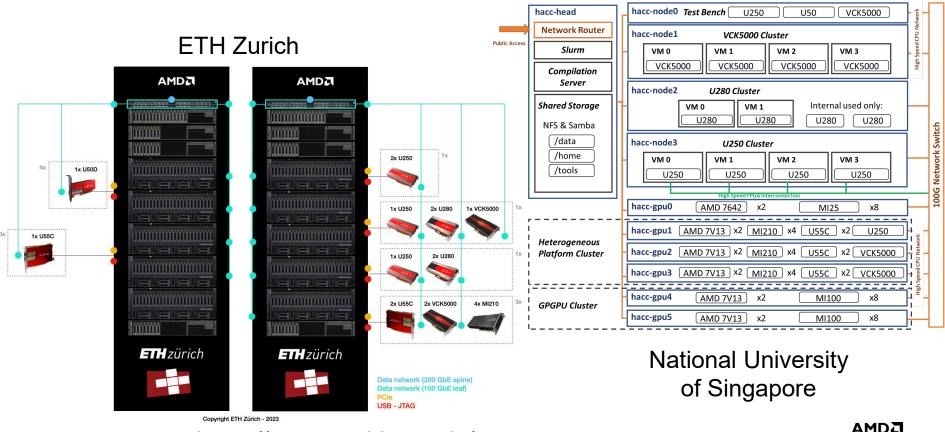

### **HACC - Heterogeneous Accelerated Compute Clusters**

together we advance\_

https://www.amd-haccs.io/

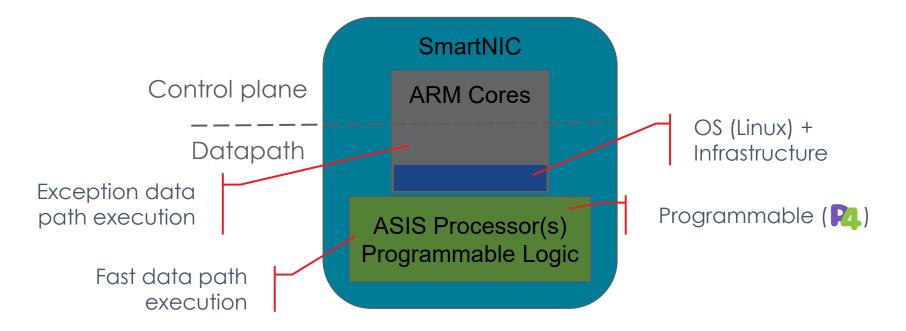

Architectures including Application Specific Instruction Set Processors

23

Intel IPU E2000

#### Upcoming

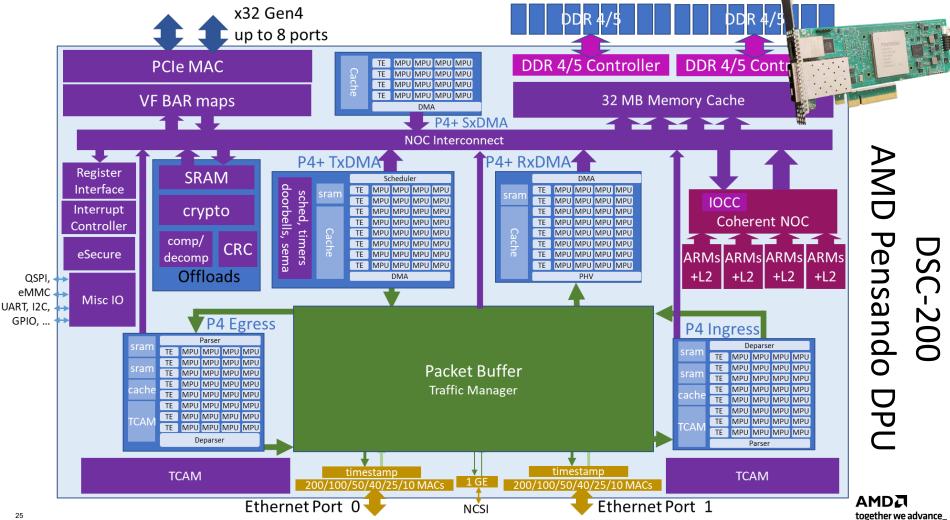

## AMD Pensando<sup>™</sup> Salina 400 Best DPU for evolving front-end networks

3rd Gen Software Compatible

400G

232 P4 MPU Multi-Services PCIe® Gen 5 2x400GE

2x DDR5 102GB/S Memory Bandwidth Up to 128 GB DDR

16 N1 ARM Cores

AMD Pensando<sup>™</sup> DPU choice for hyperscalers

#### Upcoming

## AMD Pensando<sup>™</sup> Pollara 400

Industry's first ultra ethernet consortium ready AI NIC

400 Gbps

Programmable Hardware Pipeline Up to 6x Performance Boost\* Open Ecosystem UEC Ready RDMA Reduction in Job Completion Times High Availability

#### And The Software?

0 • • • • • 1 • **0** • 0 1 0 • • **0** • **0** 1 • **1** 1 • **0** • • • • 1 • 1 0 • 0 • • • • 1 1 • • • • • • • • 0 1 101110 • 1 • • 11 • • 111 • 10 • • 11001 0 10 · 10 1 1 1 0 · · • 0 · · 1 1 1 · · · 10 1 · 0 0 0 • 1 0 • 1 · • · 0 · 1 1 · 011110011.001011...00...01 0 0 0010000010.00 • 10 1 1 • 1 1 • 000 · 0 • 0 10 1 • • • • • • 0 • • • • 0 1 • 0 • • 0 1 • 1 0 1001+ 0+ **01+ 0110** + 1011+ 1+ 0**0** + 1+ + **1** + 111+ 0 = 0 + 0 **1 1 0 - • 0 • 0 • • • 1 0 • 0 • • • • 0 1 • • • 0 0** 1 • • • **0 1 • 1 • 0 (** ) 1 · 10 · 10 · 1 · 1 · 1 0 • 1 · 0101 · • 0 • • 10 0 1 · 101 • 1 • 0 • 0 1

#### Hardware and Software Architecture at a Very High Level

# Software development is challenging

together we advance

#### An incremental path to accelerating/offloading existing applications Control Control Plane CPU Plane .... Data Plane =| ARM .... Data Plane Ξ = Control Data Plane CPU .... **E** P4 E Plane Data Plane 11111 111 .... Control Control **Data Plane** ARN

....

Plane

Ξ

Ξ P4

ARM

.... 1111

**Data Plane**

Data Plane

Plane

#### Disclaimer

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions, and typographical errors. The information contained herein is subject to change and may be rendered inaccurate for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product releases, product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. Any computer system has risks of security vulnerabilities that cannot be completely prevented or mitigated. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to the content hereof without obligation of AMD to notify any person of such revisions or changes. THIS INFORMATION IS PROVIDED 'AS IS." AMD MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE CONTENTS HEREOF AND ASSUMES NO RESPONSIBILITY FOR ANY INACCURACIES, ERRORS, OR OMISSIONS THAT MAY APPEAR IN THIS INFORMATION. AMD SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, OR FITNESS FOR ANY PARTICULAR PURPOSE. IN NO EVENT WILL AMD BE LIABLE TO ANY PERSON FOR ANY RELIANCE, DIRECT, INDIRECT, SPECIAL, OR OTHER CONSEQUENTIAL DAMAGES ARISING FROM THE USE OF ANY INFORMATION CONTAINED HEREIN, EVEN IF AMD IS EXPRESSLY ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

AMD, the AMD Arrow logo, Xilinx, and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies. Arm is a registered trademark of Arm limited (or its subsidiaries) in the US and/or elsewhere. Intel is a trademark of Intel Corporation or its subsidiaries. Cisco is a registered trademark of Cisco Systems Inc.

©2024 Advanced Micro Devices, Inc. All rights reserved.

Third-party content is licensed to you directly by the third party that owns the content and is not licensed to you by AMD. ALL LINKED THIRD-PARTY CONTENT IS PROVIDED "AS IS" WITHOUT A WARRANTY OF ANY KIND. USE OF SUCH THIRD-PARTY CONTENT IS DONE AT YOUR SOLE DISCRETION AND UNDER NO CIRCUMSTANCES WILL AMD BE LIABLE TO YOU FOR ANY THIRD-PARTY CONTENT. YOU ASSUME ALL RISK AND ARE SOLELY RESPONSIBLE FOR ANY DAMAGES THAT MAY ARISE FROM YOUR USE OF THIRD-PARTY CONTENT.

# AMDZ